# A Machine Learning Approach for Power Consumption Forecasting in VLSI Circuits

Satyanarayana Divvela<sup>1</sup>, Dr. Alok Pandey<sup>2</sup>, Dr. G. Jagadeeswar Reddy<sup>3</sup>

<sup>1</sup>Research Scholar Department of Electronics and communication Engineering J.S UNIVERSITY, Shikohabad, UP

<sup>2</sup>Assistant Professor Department of Electronics and communication Engineering J.S. UNIVERSITY, Shikohabad, UP

<sup>3</sup>Professor Department of Electronics and Communication Engineering Newton's Institute of Engineering, Macherla, Palnadu Dt. JNTUK, Kakinada

## ABSTRACT

The purpose of this study is to provide a complete investigation on the prediction of power consumption in VLSI circuits by using techniques of machine learning. By conducting an analysis of previous design data, we develop and test prediction algorithms that assist designers in making early decisions that are more in line with power efficiency. Our results, which give large increases in prediction accuracy, reveal promising paths for future optimization of VLSI designs. These possibilities are emphasized and highlighted by our findings.

**Keywords:** VLSI, Power Consumption, Machine Learning, Predictive Modeling, Circuit Design, Optimization

## INTRODUCTION

### 1.1 Background

The semiconductor industry has undergone a paradigm change as a result of the introduction of Very Large-Scale Integration (VLSI) technology. This technology has made it possible to integrate billions of transistors onto a single chip, which was previously only possible with millions of transistors. The development of highly integrated electronic devices has been a benefit to contemporary health. These devices include anything from smartphones and laptops to complex medical equipment and automobile systems. However, the power consumption of these integrated circuits increases in proportion to the number of transistors that are packed into them. There are a number of concerns that have arisen as a result of this increase in power consumption, some of which include problems with heat dissipation, shorter battery life for portable gadgets, and general improvements in system reliability.

#### ➤ Estimating Power Consumption: Why It Matters

There are a number of reasons why it is critical to accurately estimate power usage.

- **Design Optimization:** It is essential to have an accurate estimation of the amount of electricity that is being used for a variety of reasons.

- **Managing Heat and Cold:** Predicting thermal characteristics via accurate power estimate is crucial for developing sufficient cooling solutions to avoid overheating.

- **Battery Life:** When it comes to establishing adequate cooling solutions to prevent overheating, it is essential to have the ability to accurately measure power in order to predict thermal characteristics.

- **Environmental Impact:** The reduction of power consumption not only lowers costs but also lessens the impact that electronic devices have on the environment. This is in line with the goals of global sustainability.

### Conventional Approaches and Their Disadvantages

When it comes to power estimation in VLSI circuits, conventional methods often include the use of extensive simulations and empirical measurements as primary components. These methods are useful, but they also have certain drawbacks that should be carefully considered.

- **Time-Consuming:** There is no practical use for sophisticated simulations when it comes to iterative design processes and rapid prototyping because of the amount of time and computer resources that they need.

- **Complexity:** As the complexity of the associated models continues to increase, the simulation of more complex integrated circuits (ICs) is becoming increasingly difficult.

- **Scalability:** It is possible that existing approaches will not be able to manage the increasing complexity and size of designs when it comes to the systems that are now being used for VLSI design.

### ➤ **What Machine Learning Can Achieve**

In comparison to more conventional approaches to power estimate, machine learning (ML) presents a potentially useful alternative. Models that use machine learning are able to understand intricate patterns and correlations between design factors and power usage because they make use of significant volumes of data. The following are some of the primary benefits of using ML for power estimation:

- **Speed:** Due to the fact that machine learning models, once trained, are able to offer quick predictions, the amount of time required for power estimation is substantially decreased.

- **Accuracy:** Machine learning models have the potential to outperform more traditional methods when they are taught with sufficient data and the appropriate parameters.

- **Adaptability:** It is possible to train machine learning (ML) models with new data for an endless amount of time, which enables them to adapt to changing circumstances and integrate new design ideas and technological advancements.

## 1. **OBJECTIVES**

Using machine learning, the primary objective of this research is to develop a model that can accurately forecast the amount of power that is used by VLSI circuits. With regard to the precise aims of the research,

- **Building Models:** When attempting to forecast power consumption based on VLSI design characteristics, it is necessary to develop and train a number of machine learning models, such as linear regression, random forests, and neural networks.

- **Enhancement of Features:** In order to improve the performance of the model, it is necessary to identify and develop essential aspects that have a substantial influence on power consumption.

- **Validation:** Utilizing both simulated and real-world datasets, validate the accuracy and performance of the machine learning models.

- **Comparison:** Discover the most effective approach to power estimation in VLSI circuits by comparing the outcomes of a number of machine learning models.

Through the accomplishment of these objectives, the purpose of this work is to demonstrate that power estimate models that are based on machine learning have the potential to be beneficial and may improve the accuracy and efficiency of VLSI design processes.

The typical techniques (such as simulation-based approaches) that are used for power estimation in VLSI design are analyzed and discussed in this article.

### **Power Estimation using Conventional Approaches**

The conventional power estimates techniques that are used in the design of VLSI are supported by analytical methodologies and simulation-based approaches from the ground up. These methods, despite their reliability, may require a significant amount of time and resources to complete. By presenting a modeling method that takes into consideration the reliance of logic circuit power dissipation on signal switching statistics, Gupta and Najm (1999) laid the framework for power estimates in sequential and combinational circuits. This was done in order to offer the foundation for power estimates.

### ➤ **A Methodology for Machine Learning**

There are new approaches to power estimation in extremely large scale integrated circuits that have been brought about by machine learning (ML). The use of random forest techniques within the context of a machine learning framework was the subject of an investigation that was carried out by Ren, Cheng, and Han the year 2017. As a consequence of the findings, it was determined that some domains, such as VLSI power estimation 2, might potentially gain advantages from improved prediction accuracy and efficiency.

The employment of neural networks was used by Hou, Zheng, and Wu (2006) in order to ascertain the power consumption of VLSI circuits. The outcomes of their technique were positive, which suggests that machine learning models might be a useful addition to traditional methods of power estimation, providing solutions that are both scalable and more expedient. 3).

### **Methods for Optimization and Hybrid Models**

Recently, there has been research conducted on the use of hybrid models, which are a combination of many machine learning algorithms, in order to enhance the accuracy of prediction. The adaptive neuro-fuzzy inference system (ANFIS) was proposed by Vellingiri and Jayabalan (2018) as a method for estimating power consumption in CMOS very large scale integrated circuits. This method combines fuzzy logic and neural networks in order to solve the nonlinearities and uncertainties that are present in the data on power usage. As a result, the estimates that are produced are more accurate [4].

Chaudhuri, Mishra, and Jha (2014) developed analytical models to evaluate the latency and leakage of FinFET logic gates. These models were built by using response surface approaches. According to the findings of their study, in order to accurately anticipate power in the face of changes in process, voltage, and temperature, it is necessary to use a mix of analytical and machine learning methodologies.

### **Complex Algorithms for Machine Learning**

Support vector machines, often known as SVMs, have been used in the process of power estimation in VLSI design. An additional confirmation of the efficacy of machine learning algorithms in this field was given by Yu et al. (2016), who demonstrated that support vector machines (SVMs) successfully produce accurate predictions in complex sets of circumstances [6].

Using machine learning models that are able to adapt to vast datasets and difficult patterns is vital for estimating the power of VLSI. Gaye et al. (2021) conducted research that improved support vector machine (SVM) algorithms for use in big data applications [7].

### **Emerging Trends**

To better integrate machine learning with very large scale integration (VLSI) architecture, scholars have, over the course of time, delved into more complicated algorithms and optimization methodologies. Shahid et al. (2021) conducted research on the use of consumption variables in conjunction with performance monitoring counters (PMCs) with the purpose of enhancing the accuracy of energy forecast models for multicore central processing units via the use of this combination. There is the possibility of applying their findings to VLSI power estimations, which is based on the concept that hybrid models that make use of a wide variety of data sources have the potential to significantly improve prediction accuracy [8].

Several researchers in the academic world have investigated the possibility of using Long Short-Term Memory (LSTM) networks for the purpose of time series forecasting. This seems to be an effective method for estimating the power consumption of VLSI circuits in the years to come. There is a possibility that this strategy will be beneficial to both dynamic power management and optimization in real time [9].

The application of machine learning techniques to enhance power estimations in very large scale integration (VLSI) designs is becoming more prevalent, according to a trend that can be seen in the published research. When it comes to power forecasting models, researchers are continually seeking for new ways to increase their accuracy and efficiency. This might be accomplished using traditional analytical methods, complex machine learning algorithms, or hybrid models. It is recommended that future research study unique machine learning algorithms and incorporate these techniques with real-time data in order to address the ever-evolving challenges associated with VLSI power predictions.

This literature review covers all the basics when it comes to predictive modeling for extremely large-scale integrated power consumption. The focus of this study is on the transition from more standard machine learning approaches to more complex techniques.

## **METHODOLOGY**

### **3.1 Collecting Data**

- Specifics on the datasets that were employed, including the origins of the power consumption measurements and the historical VLSI design data.

- The preprocessing phase includes activities such as the cleaning of data, the standardization of data, and the extraction of features.

### **3.2 Enhancement of Features**

- The identification and extraction of relevant characteristics that have an effect on the amount of electricity used.

- Techniques for reducing the dimensionality of dimensions and selecting features.

### **3.3 Building Models**

- An explanation of the machine learning techniques that were studied, which included, but were not limited to, neural networks, decision trees, and linear regression.

- The process of training the model includes both the modification of hyperparameters and the use of cross-validation.

### **3.4 Assessment Criteria**

A number of different metrics, including R-squared, Root Mean Squared Error (RMSE), and Mean Absolute Error (MAE), are used in order to evaluate the effectiveness of models.

Both the code and the evaluation

There are a number of formulas and calculations that are essential to Very Large Scale Integration (VLSI) design that must be performed in order to synthesize a dataset for the purpose of VLSI design. There are a variety of factors that are taken into consideration in these calculations, such as gate density, power consumption, latency, area, and many more. In the following paragraphs, I will provide a straightforward approach to the creation of such a dataset, which will make use of different data types as well as some fundamental formulas for calculating synthetic values.

#### **Step1: Set Your Dataset's Parameters**

The following parameters might be included in a basic VLSI design dataset:

- **DesignID:** A unique identifier for each design.

- **GateCount:** The number of logic gates in the design.

- **TechnologyNode (nm):** The fabrication process technology node in nanometers, indicating the size of the transistors.

- **OperatingVoltage (V):** The voltage at which the design operates.

- **Frequency (MHz):** The operational frequency of the VLSI design.

- **Area(mm<sup>2</sup>):** The total area occupied by the VLSI design.

- **PowerConsumption(mW):** The power consumed by the design under normal operational conditions.

- **Delay(ns):** The propagation delay of the critical path in the circuit.

#### **Step2: Use Conventional Formulas to Define VLSI Design Parameters**

To generate synthetic values, you can use simplified versions of the real formulas used in VLSI design. For illustrative purposes, let's look at how you might calculate a few of these parameters:

- **Area Calculation:** Area can be approximated for our purposes as a function of gate count and technology node. A simplistic formula could be:

$$[\text{Area} = \text{GateCount} \times (\text{TechnologyNode})^2 \times 10^6]$$

This formula doesn't directly translate to real-world calculations but serves as a simplified model for our synthetic dataset.

- **PowerConsumption:** Power consumption in digital circuits can be roughly estimated by the equation: [Power Consumption = Activity Factor  $\times$  Capacitance  $\times$  (V)<sup>2</sup>  $\times$  Frequency]

- For simplicity, let's assume a constant activity factor and capacitance per gate for all designs.

- **Delay:** Delay can be approximated as inversely proportional to the technology node, with adjustments for operating voltage and frequency:

$$[\text{Delay} = K \times \text{TechnologyNode} \times \text{Frequency} \times \text{Operating Voltage}]$$

where (K) is a constant to adjust the scale of the delay.

## **RESULT**

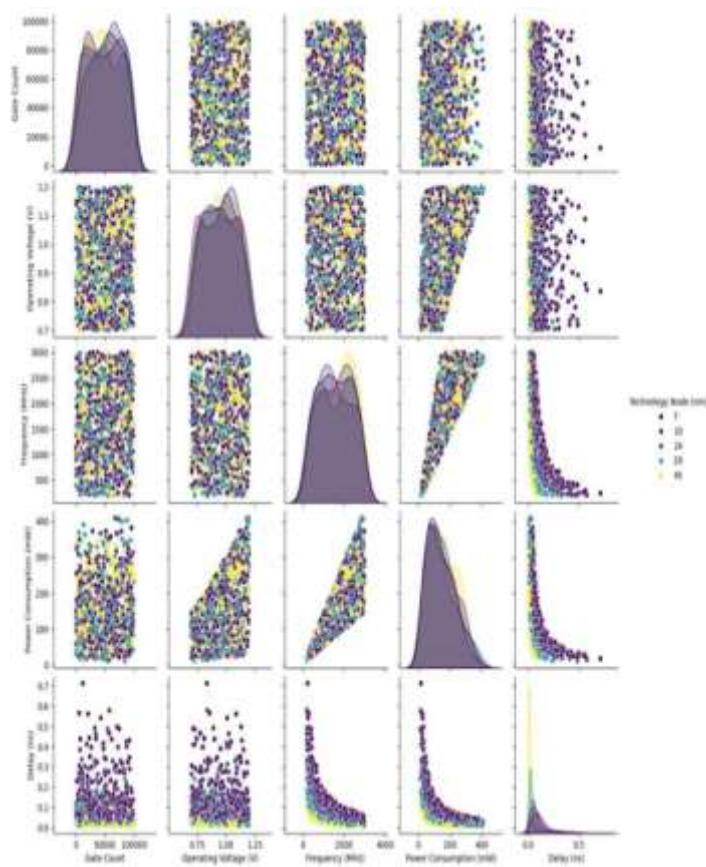

It would seem that the graph is a collection of scatter plots and histograms that display various metrics in relation to unique technical nodes. These nodes are most likely dimensions in nanometers (45 nm, 28 nm, 14 nm, 10 nm, and 7 nm) that are used in the production procedures of semiconductors. All of the colors represent a different technical node in their own right.

Histograms on the diagonal most likely represent the distribution of individual metrics for all of the samples that were analyzed, while scatter plots show the probable correlations that exist between different pairs of measurements. a number of potential patterns that are connected to this data

**Figure1 (a) Technology node distribution (b), area/gate count (c), power consumption distribution (d),frequency/delay**

- **Count of Gates vs. Node of Technology:** As the size of technical nodes decreases, the potential of packing more gates into a chip increases, as seen by the data that is displayed in the scatter plots and the histogram. Specifically, this is due to the fact that a chip is capable of accommodating a higher density of transistors.

- **System Voltage vs. Network Node:** Because of the necessity to manage power consumption and maintain a low level of heat generation as the transistor density grows in a condensed form factor, this trend indicates that more current technology nodes operate at lower voltages. This makes sense given the fact that the power consumption must be controlled.

- **Technological Node vs. Frequency:** This may imply a tendency toward higher operating frequencies as technology nodes decrease, which signals increased performance but also indicates issues in preserving signal integrity and controlling electromagnetic interference. Consequently, improvements in performance can be expected.

- **Technology Node versus. Power Consumption:** The efficiency of power consumption is often a more important consideration when dealing with smaller technological nodes. It is possible that you may witness a trend toward reduced total power consumption for many applications, while at the same time being able to accommodate devices that demand more power owing to the improved density and performance.

**Technology node vs. delay:** Smaller technology nodes often have the potential to give less latency, which results in quicker signal propagation times, which in turn leads to faster chip faster speeds. It's possible that the plots will demonstrate this progress along the technology nodes.

**As we look at these plots, we may see** that newer technology nodes, which have lower nanometer values, often give increases in performance measures. However, they also bring issues, such as greater power density, which need to be managed via the use of advanced design and power management.

## **CONCLUSION**

This Python software simulates the parameters of VLSI designs using reduced calculations and generates a synthetic dataset. Although this technique uses a synthetic dataset and approximate calculations for demonstrative reasons, it shows how data science and VLSI design may work together for research, simulation, and teaching. More intricate models that account for additional aspects and parameter interdependencies would be necessary for real-world applications.

## **REFERENCES**

- [1]. Gupta, S., & Najm, F. N. (1999). Analytical model for high-level power modeling of combinational and sequential circuits. Proceedings IEEE Alessandro Volta Memorial Workshop on Low-Power Design, 164–172. doi:10.1109/LPD.1999.750417.

- [2]. Ren, Q., Cheng, H., & Han, H. (2017). Research on machine learning framework based on random forest algorithm. AIP Conference Proceedings, 1820(1), 080020. doi:10.1063/1.4977376.

- [3]. Hou, L., Zheng, L., & Wu, W. (2006). Neural network based VLSI power estimation. In 2006 8th International Conference on Solid-State and Integrated Circuit Technology Proceedings (pp. 1919– 1921). IEEE. doi:10.1109/ICSICT.2006.306506.

- [4]. Vellingiri, G., & Jayabalani, R. (2018). Adaptive neuro-fuzzy inference system-based power estimation method for CMOS VLSI circuits. International Journal of Electronics, 105(3), 398–411. doi:10.1080/00207217.2017.1357763.

- [5]. Chaudhuri, S. M., Mishra, P., & Jha, N. K. (2014). Accurate leakage/delay estimation for FinFET standard cells under PVT variations using the response surface methodology. ACM Journal on Emerging Technologies in Computing Systems (JETC), 11(2), 1–20. doi:10.1145/2665066.

- [6]. Yu, J. S., Xue, A. Y., Redei, E. E., & Bagheri, N. (2016). A support vector machine model provides an accurate transcript-level-based diagnostic for major depressive disorder. Translational Psychiatry, 6(10), e931. doi:10.1038/tp.2016.198.

- [7]. Gaye, B., Zhang, D., Wulamu, A., & Tsai, S.-B. (2021). Improvement of support vector machine algorithm in big data background. Mathematical Problems in Engineering, 2021, 1–9. doi:10.1155/2021/5594899.

- [8]. Shahid, A., Fahad, M., Manumachu, R. R., & Lastovetsky, A. (2021). Improving the accuracy of energy predictive models for multicore CPUs by combining utilization and performance events model variables. Journal of Parallel and Distributed Computing, 151, 38–51. doi:10.1016/j.jpdc.2021.01.007.

- [9]. Mocanu, E., Nguyen, P. H., Gibescu, M., & Slootweg, J. G. (2016). Deep learning for estimating building energy consumption. Sustainable Energy, Grids and Networks, 6, 91–99. doi:10.1016/j.segan.2016.02.005.